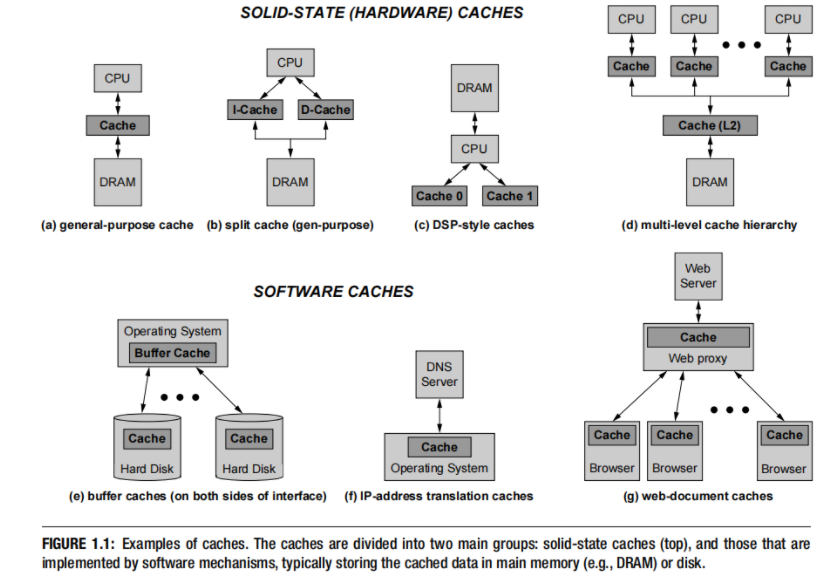

“缓存”这一概念在计算机各个层面(硬件和软件)被广泛使用,并且在不同领域中虽然具体实现不同,但核心目的是一致的:提高数据访问效率、减少延迟、提升性能。

上排展示了硬件缓存的配置,下排则展示了一些软件缓存的例子。

图 1.1(a) 展示的是一个通用处理器核心及其缓存。

软件(比如程序)认为自己直接访问的是主内存里的数据(DRAM),但实际上,缓存会自动“拦截”这些访问请求,先检查自己有没有请求的数据,如果缓存里有,就直接返回,避免去慢速的DRAM读写;如果缓存里没有,才去访问DRAM并把数据放入缓存。

图 1.1(b) 展示了通用缓存的另一种配置方式,其中缓存在逻辑上/或物理上被划分为两个独立的分区:

- 一个分区仅用于存储指令,

- 另一个分区仅用于存储数据。

对缓存进行分区可以改善其行为。例如:

- 为每个分区分别提供一条独立的总线,给它们分别配独立的总线,指令和数据可以同时高速传输,带宽大约能翻倍,处理器能更快拿到需要的内容。

- 指令通常是固定长度(比如32位),把指令缓存专门用来存这类固定长度的东西,就不用设计复杂的逻辑去支持变长的读取操作,硬件更简单,效率更高。

图 1.1(b) 描述的就是Harvard 架构的缓存配置,或者称为分离指令/数据缓存(Split I-Cache/D-Cache),这种结构常见于现代 CPU 尤其是 L1 缓存层。

这种设计的主要优势是:

- 提高并行性(可以同时取指和访数);

- 减少资源冲突;

- 提高性能,尤其对嵌入式系统和实时系统更有意义。

图 1.1(c) 展示的是另一种分区配置,这种配置在大多数数字信号处理器(DSP)架构中都可以见到。这类缓存是内存空间的扩展,不像前面提到的两种缓存组织方式,它们对软件不是透明的。这里需要注意的一个主要点是:这两个分区都用于存储数据。这种配置在 DSP 中是非常有价值的,因为许多 DSP 算法(例如有限冲击响应(FIR)滤波器等点积计算)需要非常高的数据带宽,它们在每个时钟周期中都要从内存中取出两个不同的数据操作数。所以,DSP通过这种“两个数据缓存分区”的设计,满足了高速并行读取数据操作数的需求,提高了处理效率。

图 1.1(d) 展示了一个典型的多处理器系统中的缓存层次结构(cache hierarchy)。

- 每个处理器核心都有自己私有的缓存;

- 而在连接到后备存储(DRAM)之前的最后一级缓存(Last-Level Cache, LLC)是所有核心共享的。

图 1.1(e) 展示了两种不同类型的缓存:

- 操作系统缓存:操作系统会将它从磁盘中读取的块(block)存储在主存(内存)中,作为缓冲区缓存(buffer cache)的一部分。当应用程序从文件中读取或向文件写入数据时,这些请求并不是直接交给磁盘处理,而是由缓冲区缓存来响应的。

- 磁盘自身的缓存:此外,现代磁盘本身也实现了自带缓存。这些缓存不受操作系统控制,而是自主运行的(autonomous)。

图 1.1(f) 展示了另一种由操作系统维护的缓存。

当需要将域名解析为 IP 地址时,操作系统不一定每次都直接请求 DNS 服务器。这些域名解析结果(即 DNS 映射)可以被缓存在本地,从而避免不必要的网络请求。类似地,主机(hosts)和子网(subnets)的路由信息也通常会缓存在本地。

图 1.1(g) 展示了两种不同类型的缓存:

- 浏览器缓存:每个网页浏览器通常都会维护一个本地缓存,用于存储下载过的网页文档。

这些文档通常会保存在本地磁盘上,并作为操作系统缓冲区缓存(如图 1.1(e))的一部分缓存在主存中。 - Web 代理缓存:当用户发出一个访问某个 Web 服务器的请求时,

该请求可能并不会真正发送到服务器。一个Web 代理服务器(proxy)可能会拦截这个请求,并\代表服务器直接返回响应。这种代理行为类似于图 1.1(a)、(b)、(d) 所描述的透明缓存(transparent caches)。

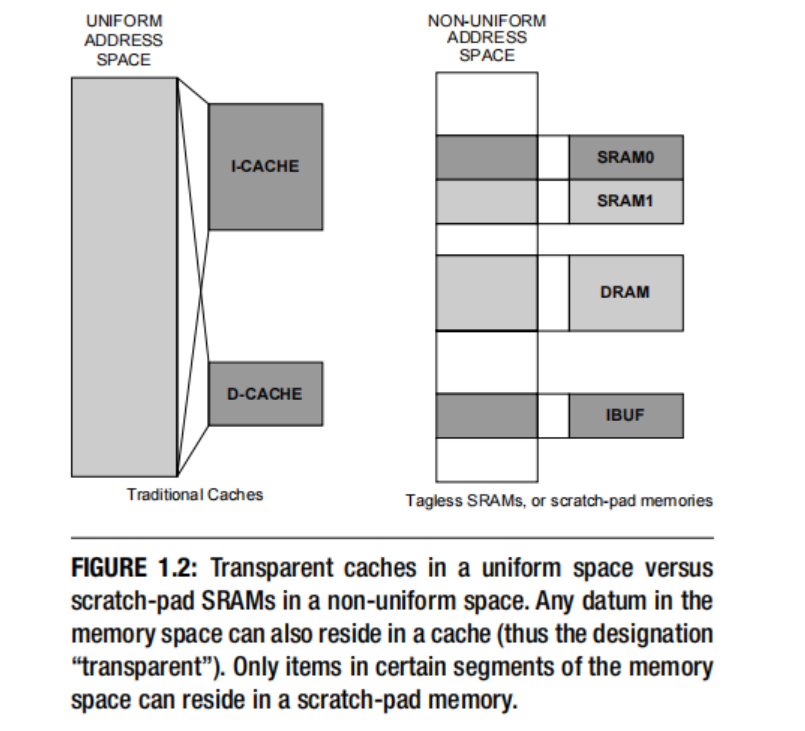

这两种机制(透明缓存 transparent cache 和 划区内存 scratch-pad memory)是如何融入微处理器的内存模型的,如图 1.2 所示,图中用的是固态内存(如处理器缓存和无标签 SRAM,tagless SRAM)作为示例。

通用内存模型(General-purpose memory model)

- 拥有单一命名空间(single namespace),这个命名空间由所有内存结构共享。

- 命名空间中的任意数据项(datum)都可以出现在任意缓存中。

- 举例来说:你可以通过一个虚拟地址访问主存中的数据,但该地址的数据也可能被缓存到了 L1、L2、L3 中——它们在逻辑上是等价的。

划区内存模型(Scratch-pad memory model)

-

命名空间被显式划分,用于直接寻址不同的物理存储结构。

-

举个例子:右侧的 DSP(数字信号处理器)内存模型中,系统的内存结构(如 RAM、ROM、SRAM 等)被明确放置在命名空间中不同的、互不重叠的位置(disjunct locations)。

-

一个具体的地址只能映射到一个特定的物理存储设备。

-

与透明缓存不同,同一个地址不会同时代表缓存和主存中的副本——地址是绝对的,指向固定的地方。

缓存单一性与独立性

│

├─ 缓存定义的灵活性

│ ├─ 单一缓存实体

│ └─ 多个独立缓存集合

│

├─ 同层级缓存整体分析

│ ├─ 多核CPU的L1缓存

│ ├─ 磁盘缓存

│ └─ 浏览器缓存

│

├─ 多层缓存视为单一实体

│ ├─ L1、L2、L3层级缓存

│ └─ 与主存(后端存储)区分

│

├─ 单一缓存拆分分析

│ ├─ 独立缓存块

│ └─ 例如图1.1(a)和(f)缓存

│

├─ 跨领域通用与互借鉴

│ ├─ 统一“缓存”概念

│ └─ 不同领域解决方案融合

│

└─ 目标与意义

├─ 建立统一分析框架

└─ 帮助设计和理解缓存系统